Super I/O

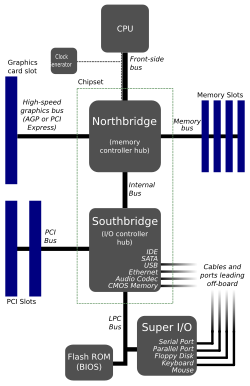

Diagram of a motherboard, which supports many on-board peripheral functions as well as several expansion slots.

ITE Super I/O chip (IT8712F)

SMSC (now Microchip) Super I/O chip (FDC37M813) on IBM motherboard

Super I/O is a class of I/O controller integrated circuits that began to be used on personal computer motherboards in the late 1980s, originally as add-in cards, later embedded on the motherboards. A super I/O chip combines interfaces for a variety of low-bandwidth devices. The functions below are usually provided by the super I/O if they are on the motherboard:

A full set of IBM PC/AT-compatible peripherals, excepting the interrupt and DMA controllers:

- A floppy-disk controller[1]

- An IEEE 1284-compatible parallel port[1] (commonly used for printers)

- One or more 16C550-compatible serial port UARTs[1]

- An embedded controller and/or keyboard controller that is sometimes connected to a PS/2 keyboard and/or mouse interface.

- An Intel 8254-compatible programmable interval timer

- A battery-backed real-time clock and nonvolatile BIOS memory

Most chips include some additional low-speed devices, such as:

- Temperature, voltage, and fan speed sensors[2][3]

- Chassis intrusion detection

Pulse-width modulation fan speed control[4]

- A serial BIOS ROM interface (if the ROM is not directly on the LPC bus itself)

- An infrared port controller

- A game port (not provided by modern super I/O chips anymore because Windows XP is the last Windows OS to support a game port)

- A watchdog timer

- A consumer IR receiver

- a MIDI port

- Some general-purpose input/output pins

Legacy Plug and Play support for the included devices

By combining many functions in a single chip, the number of parts needed on a motherboard is reduced, thus reducing the cost of production.

The original super I/O chips communicated with the central processing unit via the Industry Standard Architecture (ISA) bus. With the evolution away from ISA towards use of the Peripheral Component Interconnect (PCI) bus, the Super I/O chip was often the biggest remaining reason for continuing inclusion of ISA on the motherboard.

Modern super I/O chips use the Low Pin Count (LPC) bus instead of ISA for communication with the Central processing unit. This normally occurs through an LPC interface on the southbridge chip of the motherboard.

Companies that make super I/O controllers include Nuvoton (formerly Winbond),[1]ITE,[1][3] Fintek,[5] and Microchip Technology. National Semiconductor used to make super I/O controllers but sold that business to Winbond, which already had a competing super I/O controller business. In 2005, Winbond then spun off its logic businesses to a wholly owned subsidiary, Nuvoton. SMSC made super I/O chips and then got acquired by Microchip Technology.

See also

- envsys

- hw.sensors

lm_sensors contains a tool named sensors-detect that can also detect which Super I/O is used on a mainboard- SpeedFan

References

^ abcde "Super I/O Chip Examples". Archived from the original on 2008-05-18..mw-parser-output cite.citation{font-style:inherit}.mw-parser-output .citation q{quotes:"""""""'""'"}.mw-parser-output .citation .cs1-lock-free a{background:url("//upload.wikimedia.org/wikipedia/commons/thumb/6/65/Lock-green.svg/9px-Lock-green.svg.png")no-repeat;background-position:right .1em center}.mw-parser-output .citation .cs1-lock-limited a,.mw-parser-output .citation .cs1-lock-registration a{background:url("//upload.wikimedia.org/wikipedia/commons/thumb/d/d6/Lock-gray-alt-2.svg/9px-Lock-gray-alt-2.svg.png")no-repeat;background-position:right .1em center}.mw-parser-output .citation .cs1-lock-subscription a{background:url("//upload.wikimedia.org/wikipedia/commons/thumb/a/aa/Lock-red-alt-2.svg/9px-Lock-red-alt-2.svg.png")no-repeat;background-position:right .1em center}.mw-parser-output .cs1-subscription,.mw-parser-output .cs1-registration{color:#555}.mw-parser-output .cs1-subscription span,.mw-parser-output .cs1-registration span{border-bottom:1px dotted;cursor:help}.mw-parser-output .cs1-ws-icon a{background:url("//upload.wikimedia.org/wikipedia/commons/thumb/4/4c/Wikisource-logo.svg/12px-Wikisource-logo.svg.png")no-repeat;background-position:right .1em center}.mw-parser-output code.cs1-code{color:inherit;background:inherit;border:inherit;padding:inherit}.mw-parser-output .cs1-hidden-error{display:none;font-size:100%}.mw-parser-output .cs1-visible-error{font-size:100%}.mw-parser-output .cs1-maint{display:none;color:#33aa33;margin-left:0.3em}.mw-parser-output .cs1-subscription,.mw-parser-output .cs1-registration,.mw-parser-output .cs1-format{font-size:95%}.mw-parser-output .cs1-kern-left,.mw-parser-output .cs1-kern-wl-left{padding-left:0.2em}.mw-parser-output .cs1-kern-right,.mw-parser-output .cs1-kern-wl-right{padding-right:0.2em}

^ Constantine A. Murenin (2007-04-17). Generalised Interfacing with Microprocessor System Hardware Monitors. Proceedings of 2007 IEEE International Conference on Networking, Sensing and Control, 15–17 April 2007. London, United Kingdom: IEEE. doi:10.1109/ICNSC.2007.372901. ISBN 1-4244-1076-2. IEEE ICNSC 2007, pp. 901—906.

^ ab Julien Bordet (2003). "it — ITE IT8705F/12F/16F and SiS SiS950 Super I/O Hardware Monitor". BSD Cross Reference. DragonFly BSD. Retrieved 2019-03-07. Lay summary.

^ Constantine A. Murenin (2010-05-21). OpenBSD Hardware Sensors — Environmental Monitoring and Fan Control (MMath thesis). University of Waterloo: UWSpace. hdl:10012/5234. Document ID: ab71498b6b1a60ff817b29d56997a418.

^ Alexander Yurchenko (2005). "fins — Fintek F71805F LPC Super I/O". BSD Cross Reference. OpenBSD. Retrieved 2019-03-07. Lay summary.

External links

Superiotool is a Linux user-space tool to detect which Super I/O is used on a mainboard, and it can provide detailed information about its register contents.